Northwestern Jniversity

UNIVERSITY

### Introduction

- Simulating long-duration workloads on gem5 takes prohibitively long time.

- Even with gem5's fastest Atomic model, reaching a steady state can be a timeconsuming task.

| Application /<br>Host Runtime | <pre># Instruction (Billions)</pre> | Approximate<br>Simulation Time |

|-------------------------------|-------------------------------------|--------------------------------|

| Linux Boot                    | 2.4 B                               | ~24 min                        |

| 1 second                      | 2 B                                 | ~20 min                        |

| 1 minute                      | 120 B                               | ~20 hours                      |

| 10 minutes                    | 1200 B                              | ~8 days                        |

Approx. simulation time with gem5's Atomic CPU

**Checkpoint State**

**CPU Registers**

Physical Memory

Hard Disk Image

Controller State

A minimal subset of hardware state needed to create resumable checkpoint

# **Platform Configuration**

- Device mapping in gem5 achieved through QEMU Virtual Configuration.

- The configuration is exposed as new system configuration.

- GIC v2 is enabled to support Apple M1 Checkpoints.

- Disk is attached as VirtIO device.

- The subset of VirtIO features supported by gem5 should be used during QEMU emulation.

# **QPoints: QEMU to gem5 ARM** Full System Checkpointing Bhargav Reddy Godala, Ishita Chaturvedi, Yucan Wu, Simone Campanoni<sup>\*</sup>, David I August

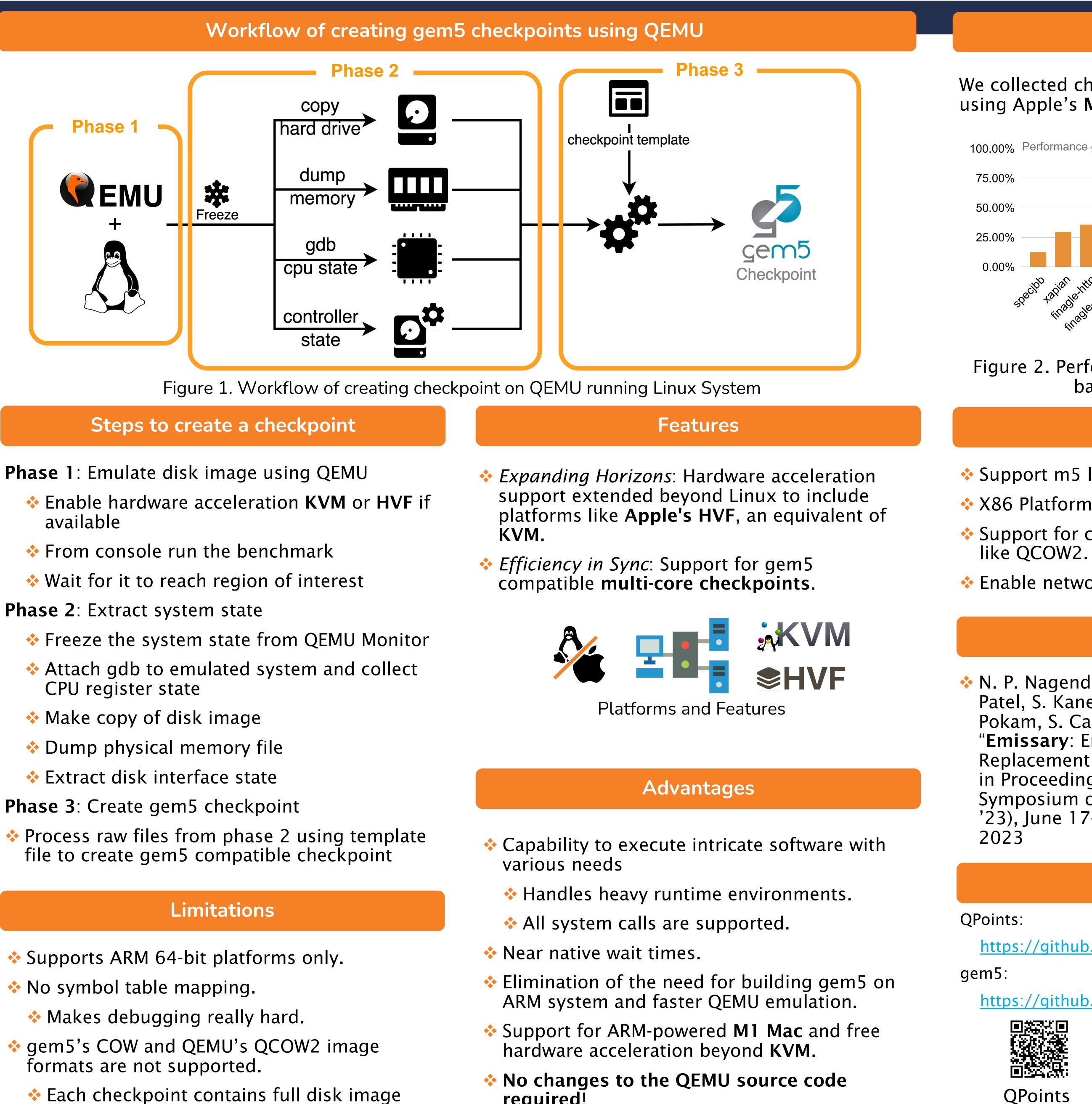

**Phase 2**: Extract system state

Phase 3: Create gem5 checkpoint

Process raw files from phase 2 using template

- Supports ARM 64-bit platforms only.

- gem5's COW and QEMU's QCOW2 image

Each checkpoint contains full disk image

required!

### Results

### We collected checkpoints of 13 benchmarks using Apple's M1 Mac mini (HVF acceleration)

100.00% Performance gain of FDIP (in %) over No FDIP baseline

Figure 2. Performance gain of FDIP over No FDIP baseline of 13 workloads

### **Future Work**

Support m5 like utility.

X86 Platform Support.

Support for compressed disk image formats

Enable network device support.

# **Published Works**

N. P. Nagendra, B. R. Godala, I. Chaturvedi, A. Patel, S. Kanev, T. Moseley, J. Stark, G. A. Pokam, S. Campanoni, and D. I. August, "Emissary: Enhanced Miss Awareness Replacement policy for I2 instruction caching," in Proceedings of the 50<sup>th</sup> Annual International Symposium on Computer Architecture (ISCA) '23), June 17–21, 2023, Orlando, FL, USA,

# Links

https://github.com/PrincetonUniversity/QPoints

https://github.com/PrincetonUniversity/gem5\_FDIP

gem5