#### WIFI PW: hotel 900

The gem5 architecture simulator

A tutorial for HPCA '23, presented by the Bobby R. Bruce

### Today's Agenda

#### Introduction (8:30 to 9:00)

- What is gem5?

- What can gem5 be used for?

- Nomenclature

- Obtaining and building gem5

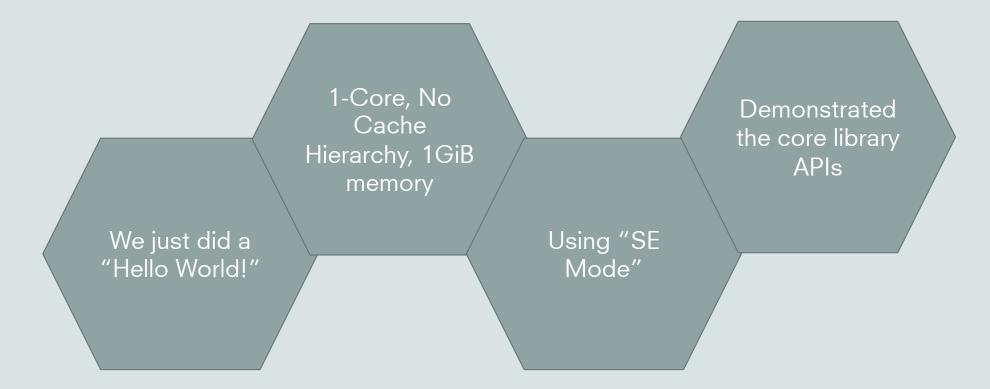

#### <u>"Hello World" in gem5 (9:00 to 9:30)</u>

- Running a "Hello World" binary in SE Mode

- How does gem5 work?

- Discrete Event Simulation

- SimObejects

#### gem5 standard library (9:30 to 10:50)

- What is it?

- Where is it?

- Gem5 Resources

- Coffee Break at somepoint.

- Understanding the stats.

- Creating a traffic generator.

- Creating a FS simulation.

- The Simulator Module

cem5

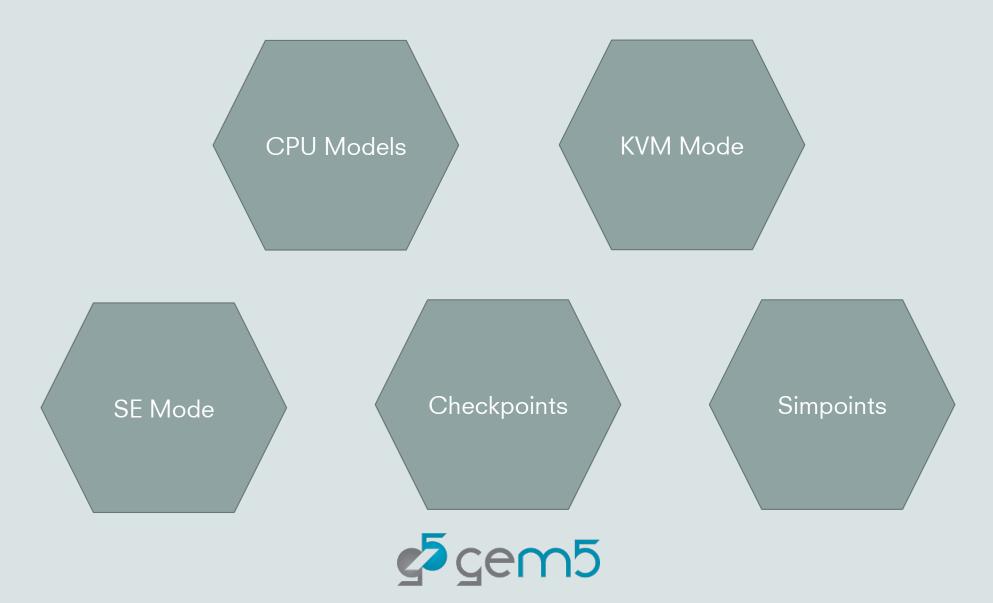

Checkpoints

What can we do?

• Simpoints and Looppoints

#### The GPU Model (11:20 to 12:05)

Speeding things up (10:50 to 11:20)

WIFI PW: hotel 900

<u>Wrap-up</u> (12:05-12:15)

Tutorial on Looppoints in the afternoon (Outremont 1)

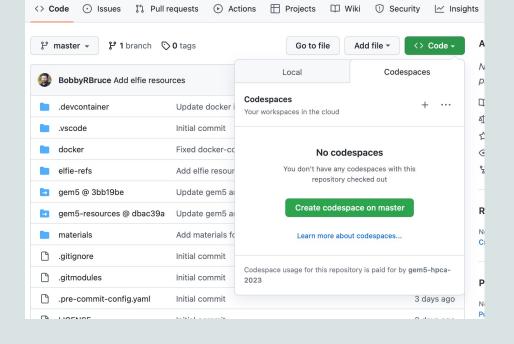

#### **GitHub Codespaces**

#### WIFI PW: hotel 900

#### https://github.com/gem5-hpca-2023/gem5-tutorial-codespace

"Code" -> "Codespaces" -> "Create Codespace on master"

This will take a minute to load a Visual Studio Code environment in your web-browser.

#### GitHub Codespaces

"materials" contains everything you need.

The "ALL/gem5.fast" binary comes pre-built and installed as "gem5"

**⊈**gem5

This is completely open source. Feel free to pull a copy.

### What is gem5?

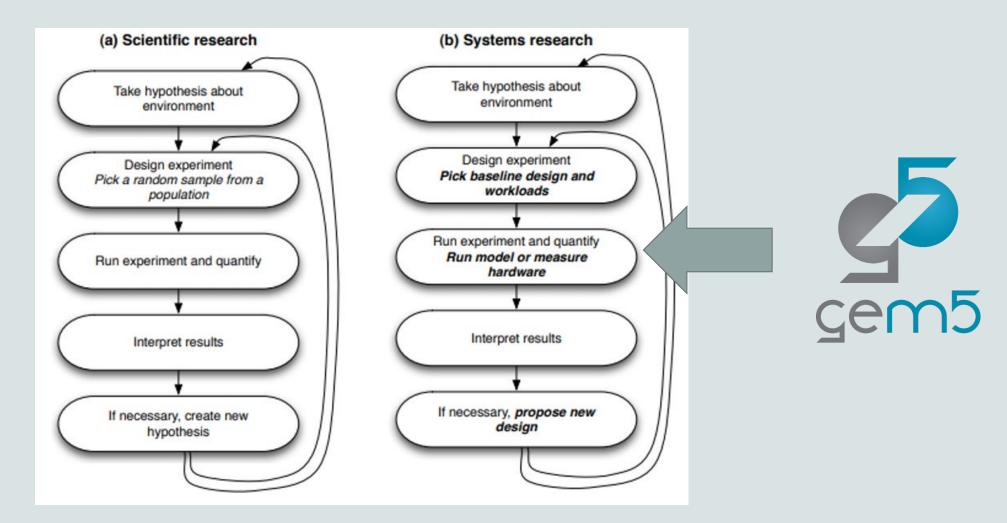

The gem5 architecture simulator provides a platform for evaluating computer systems by modeling the behavior of the underlying hardware. It enables researchers to simulate the performance and behavior of complex computer systems, including the CPU, memory system, and interconnects. This makes it possible to study the performance of different microarchitectural and architectural choices, as well as the effects of different workloads, without having to build and test real systems.

By ChatGPT

#### A little bit of history

#### A true public infrastructure project

#### Who uses gem5, and why?

#### Education

Problem: Students need to learn to design hardware but don't have a multibillion-dollar factory

#### Research

#### Researchers

We recently surveyed the top architecture conferences and found:

- 70% of all computer architecture research utilizes simulation.

- The gem5 simulator is by-far the most popular.

Room for improvement: Most users still "roll their own" simulation software. Only 20% use gem5 directly. We want to go above 50% by 2027.

#### Industry

?

Really, we don't know exactly. We don't track users and industrial users seldom make themselves known.

#### Industry

Big players we know use it

# ARM

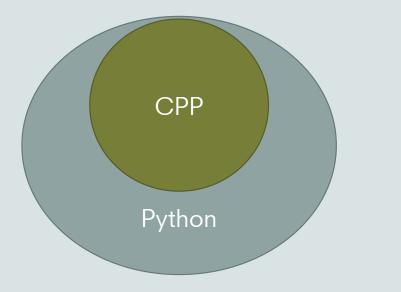

#### What languages do we use?

Your simulation configuration is written in Python which interacts with the core CPP simulator.

In this tutorial we'll be working solely at the level of Python.

Adding CPP code is necessary for extending gem5's capabilities.

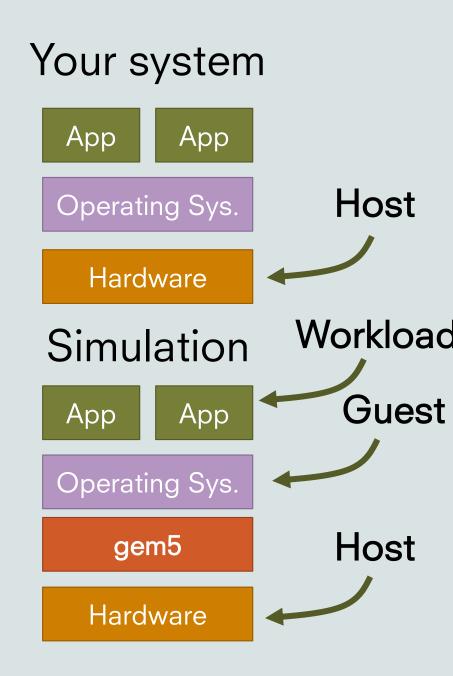

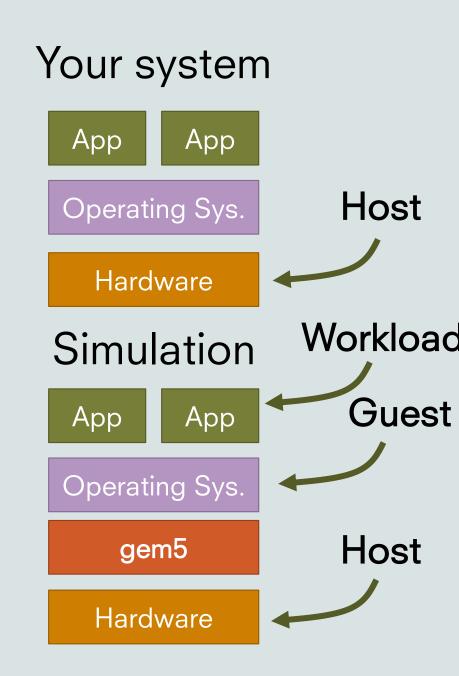

#### Nomenclature

Host: the actual hardware you're using

Simulator: Runs on the host Exposes hardware to the guest

**Guest:** Code running on *simulated* hardware OS running on gem5 is guest OS gem5 is simulating hardware

Simulator's code: Runs natively executes/emulates the guest code

Guest's code: (or benchmark, workload, etc.) Runs on gem5, not on the host.

### Nomenclature

Host: the actual hardware you're using

Simulator: Runs on the host Exposes hardware to the guest

#### Simulator's performance:

Time to run the simulation on host Wallclock time as you perceive it

#### Simulated performance:

Time predicted by the simulator Time for guest code to run on simulator

#### Let's hit the ground running

This example will show:

- 1. How someone obtains gem5.

- 2. How you build it.

- 3. Running a very basic "Hello World" simulation.

### Downloading/building gem5

- > git clone https://gem5.googlesource.com/public/gem5

- > cd gem5

- > scons build/ALL/gem5.opt -j<number of threads>

stable: The default branch for gem5. Updated at stable releases.

**develop** is updated more frequently (>1 per day)

### Write a "hello world!" configuration (in Python!)

Open "materials/hello-world.py".

We have provided the imports:

| 1 | <pre>from gem5.components.boards.simple_board import SimpleBoard</pre>             |

|---|------------------------------------------------------------------------------------|

| 2 | <pre>from gem5.components.cachehierarchies.classic.no_cache import NoCache</pre>   |

| 3 | <pre>from gem5.components.memory import SingleChannelDDR3_1600</pre>               |

| 4 | <pre>from gem5.components.processors.simple_processor import SimpleProcessor</pre> |

| 5 | <pre>from gem5.components.processors.cpu_types import CPUTypes</pre>               |

| 6 | <pre>from gem5.resources.resource import obtain_resource</pre>                     |

| 7 | <pre>from gem5.simulate.simulator import Simulator</pre>                           |

| 8 | from gem5.isas import ISA                                                          |

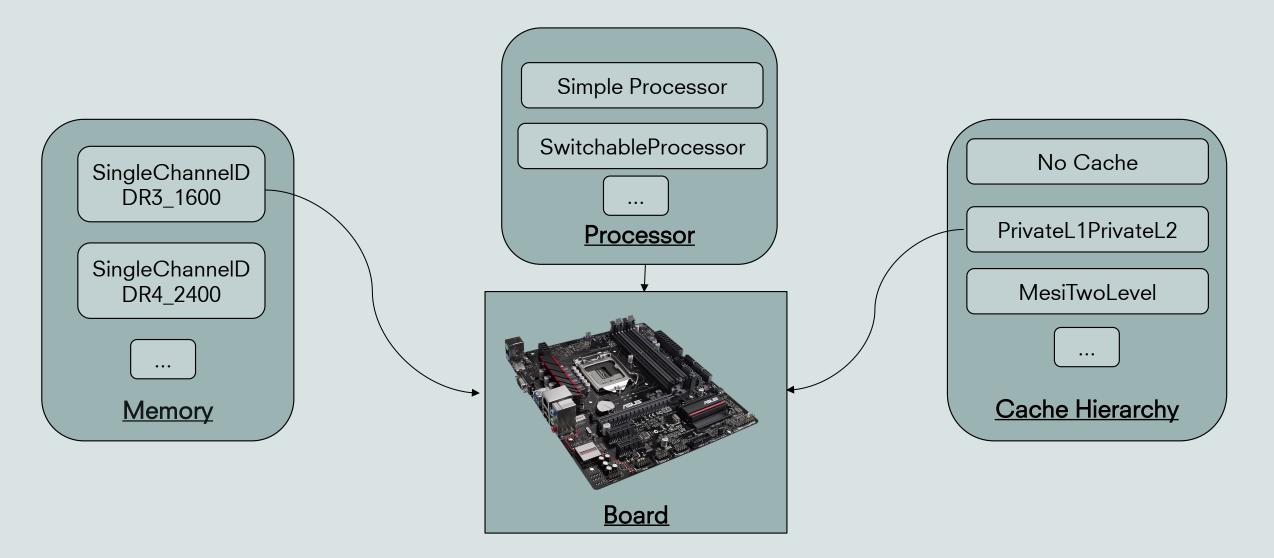

#### "hello world!": Obtaining the components

- 10 # Obtain the components.

- 11 cache\_hierarchy = NoCache()

- 12 memory = SingleChannelDDR3\_1600("1GiB")

- 13 processor = SimpleProcessor(cpu\_type=CPUTypes.ATOMIC, num\_cores=1, isa=ISA.X86)

#### "hello world!": Adding to the board!

| 14 | #Add them to the board.                     |

|----|---------------------------------------------|

| 15 | board = SimpleBoard(                        |

| 16 | clk_freq="3GHz",                            |

| 17 | processor=processor,                        |

| 18 | memory=memory,                              |

| 19 | <pre>cache_hierarchy=cache_hierarchy,</pre> |

| 20 | )                                           |

#### "hello world!": Obtain the resource

- 23 # Obtain a binary to run via gem5-resources.

- 24 binary = obtain\_resource("x86-hello64-static")

- 25 board.set\_se\_binary\_workload(binary)

#### "hello world!": Load the board to the simulator

#### 26 # Setup the Simulator and run the simulation. 27 simulator = Simulator(board=board) 28 simulator.run()

#### "hello world!": In full

from gem5.components.boards.simple board import SimpleBoard 1 from gem5.components.cachehierarchies.classic.no cache import NoCache 2 from gem5.components.memory.single channel import SingleChannelDDR3 1600 3 from gem5.components.processors.simple processor import SimpleProcessor 4 from gem5.components.processors.cpu types import CPUTypes 5 from gem5.resources.resource import Resource 6 from gem5.simulate.simulator import Simulator 7 8 # Obtain the components. 9 cache hierarchy = NoCache() 10 memory = SingleChannelDDR3 1600("1GiB") 11 processor = SimpleProcessor(cpu type=CPUTypes.ATOMIC, num cores=1) 12 13 14 #Add them to the board. 15 board = SimpleBoard( clk freq="3GHz", 16 17 processor=processor, 18 memory=memory, cache hierarchy=cache hierarchy, 19 20 21 22 # Set the workload. 23 binary = Resource("x86-hello64-static") 24 board.set se binary workload(binary) 25 26 # Setup the Simulator and run the simulation. simulator = Simulator(board=board) 27 simulator.run() 28

A full example can be found in "materials/complete/hello-world.py"

#### "hello world": Let's run it!

#### > gem5 materials/hello-world.py

Resource 'x86-hello64-static' was not found locally. Downloading to '/home/bbruce/.cache/gem5/x86-hello64-static'...

Finished downloading resource 'x86-hello64-static'.

warn: The simulate package is still in a beta state. The gem5 project does not guarantee the APIs within this package will remain consistent across upcoming releases.

Global frequency set at 100000000000 ticks per second

build/X86/mem/mem\_interface.cc:791: warn: DRAM device capacity (8192 Mbytes) does not match the address range assigned (1024 Mbytes)

0: board.remote gdb: listening for remote gdb on port 7001

build/X86/sim/simulate.cc:194: info: Entering event queue @ 0. Starting simulation...

build/X86/sim/syscall\_emul.hh:1014: warn: readlink() called on '/proc/self/exe' may yield unexpected results in various settings.

Returning '/scr/bbruce/.cache/gem5/x86-hello64-static' build/X86/sim/mem\_state.cc:443: info: Increasing stack size by one page. Hello world!

#### Wait, what just happened?

#### Ok, but how does it work?

Modern systems are very complex, and the design of gem5 simulations reflects this.

> However, at its core, the simulator builds on a relatively simple model.

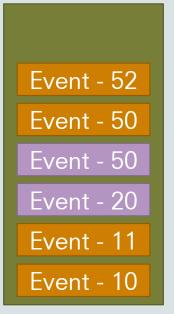

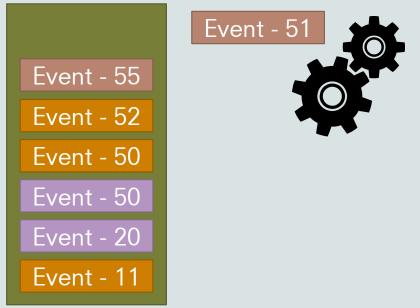

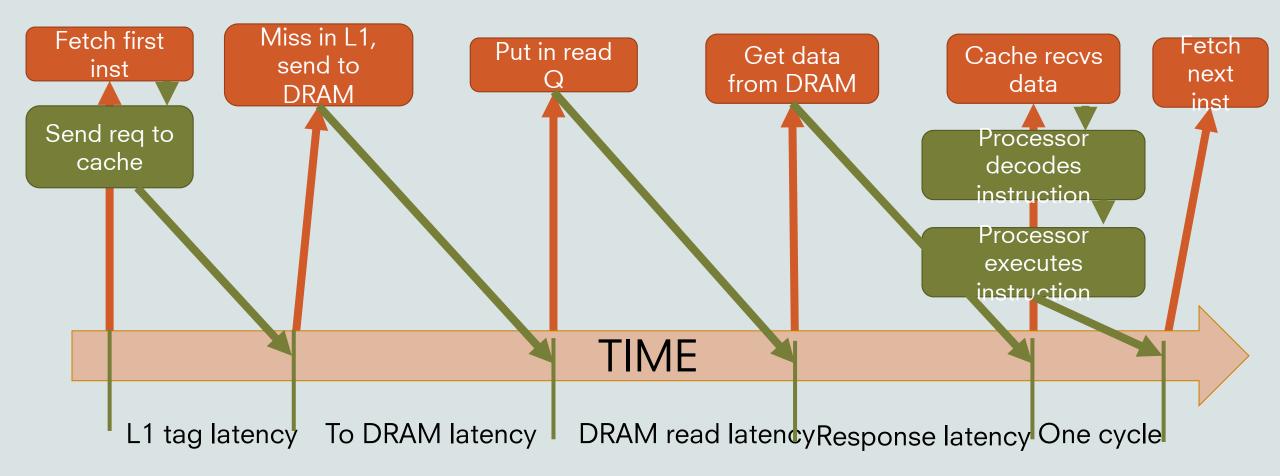

## At its core: it's a discrete event simulator

gem5 is a discrete event simulator

#### **Event Queue**

- 1) Event at head dequeued

- 2) Event executed

- 3) More events queued

## At its core: it's a discrete event simulator

gem5 is a **discrete event simulator** Event Queue

- 1) Event at head dequeued

- 2) Event executed

- 3) More events queued

### Discrete event simulation example

### Discrete event simulation

"Time" needs a unit In gem5, we use a unit called "Tick"

Need to convert a simulation "tick" to user-understandable time

E.g., seconds

This is the global simulation tick rate Usually this is 1 ps per tick or 10<sup>12</sup> ticks per second

### Ok, but how do you schedule these events?

While some are incredibly complex, at their core they only do two things:

- 1. Schedule events and process events.

- 2. Talk to other SimObjects.

#### It's hard to scale this...

When done without the library you must define *every part* of your simulation.

This allows for maximum flexibility but can mean creating 100s of lines of Python to create even a basic simulation.

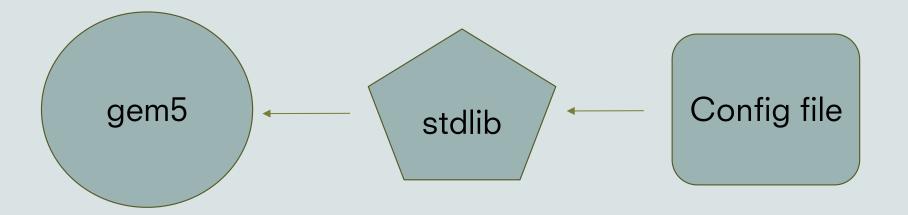

## The solution: The gem5 standard library

The stdlib is a library which allows for users to quickly create systems with pre-built components.

The stdlib's module architecture allows for components (e.g. a memory system or a cache hierarchy setup) to be quickly swapped in and out without radical redesign.

#### The stdlib modular metaphor

### The modular architecture

## Where to find stuff: The directory structure

# Where to find stuff : Importing in a script

- ∨ 📹 gem5 ✓ is components > 📫 boards > 📫 chi 🗸 📹 classic > 📫 caches 🥏 \_\_init\_\_.py abstract\_classic\_cache\_hierarchy.py no\_cache.py private\_l1\_cache\_hierarchy.py private\_l1\_private\_l2\_cache\_hierarchy.py > 📫 ruby 👌 \_\_init\_\_.py abstract\_cache\_hierarchy.py abstract\_two\_level\_cache\_hierarchy.py > 📫 memory > i processors nit\_.py > 📫 prebuilt

- > 💼 resources

- > 📹 simulate

- 🔉 🙀 utils

| 1 | <pre>from gem5.components.boards.simple board import SimpleBoard</pre>              |

|---|-------------------------------------------------------------------------------------|

| 2 | <pre>from gem5.components.cachehierarchies.classic.no_cache import NoCache</pre>    |

|   | <pre>from gem5.components.memory.single channel import SingleChannelDDR3_1600</pre> |

| 4 | <pre>from gem5.components.processors.simple processor import SimpleProcessor</pre>  |

| 5 | <pre>from gem5.components.processors.cpu types import CPUTypes</pre>                |

| 6 | from gem5.resources.resource import Resource                                        |

|   |                                                                                     |

from gem5.simulate.simulator import Simulator

7

## Let's go back and loop at our script again

from gem5.components.boards.simple board import SimpleBoard 1 from gem5.components.cachehierarchies.classic.no cache import NoCache 2 from gem5.components.memory.single channel import SingleChannelDDR3 1600 3 from gem5.components.processors.simple processor import SimpleProcessor 4 from gem5.components.processors.cpu types import CPUTypes 5 from gem5.resources.resource import Resource 6 from gem5.simulate.simulator import Simulator 7 8 # Obtain the components. 9 cache hierarchy = NoCache() 10 memory = SingleChannelDDR3 1600("1GiB") 11 processor = SimpleProcessor(cpu type=CPUTypes.ATOMIC, num cores=1) 12 13 14 #Add them to the board. 15 board = SimpleBoard( clk freq="3GHz", 16 processor=processor, 17 18 memory=memory, cache hierarchy=cache hierarchy, 19 20 21 22 # Set the workload. binary = Resource("x86-hello64-static") 23 24 board.set se binary workload(binary) 25 # Setup the Simulator and run the simulation. 26 simulator = Simulator(board=board) 27 simulator.run() 28

## gem5 Resources

- gem5 resources is a repository providing sources for artifacts that are known to be compatible with gem5.

- These resources are not necessary for the compilation or running gem5 but may aid users in running simulations. E.g.: disk images, kernels, applications, cross-compilers, etc.

- Resources are held on gem5's Google Cloud Bucket, and sources for these resources are found at: <u>https://gem5.googlesource.com/public/gem5-resources/</u>

- The stdlib can be used to automatically obtain and use these resources.

- <u>https://resources.gem5.org/resources.json</u>

# Looking up gem5 Resources

https://resources.gem5.org/resources.json

```

1 "resources": [

"resources": [

2

3

{

"type": "resource",

4

"name" : "riscv-disk-img",

5

"documentation" : "A simple RISCV disk image based on busybox.",

6

7

"architecture": "RISCV",

"is zipped" : true,

8

"md5sum" : "d6126db9f6bed7774518ae25aa35f153",

9

"url": "{url_base}/images/riscv/busybox/riscv-disk.img.gz",

10

"source" : "src/riscv-fs",

11

"additional metadata" : {

12

"root partition": null

13

14

15

},

```

This is all machine-reachable for now. We're working on a webportal.

# Obtaining Resources in the stdlib

This complete script can be found in "materials/obtain-resources.py"

- 1 from gem5.resources.resource import obtain\_resource

2

3 resource = obtain\_resource("riscv-disk-img")

4

- 5 print(f"The resource is available at {resource.get\_local\_path()}")

> gem5 materials/obtain-resources.py

## Obtaining Resources in the stdlib

Resource 'riscv-disk-img' was not found locally. Downloading to '/home/bbruce/.cache/gem5/riscv-disk-img.gz'... Finished downloading resource 'riscv-disk-img'. Decompressing resource 'riscv-disk-img' ('/home/bbruce/.cache/gem5/riscv-disk-img.gz')... Finished decompressing resource 'riscv-disk-img'. The resources is available at /home/bbruce/.cache/gem5/riscv-disk-img bbruce@liberty:~/Desktop/gem5-tutorial/gem5\$ ./build/X86/gem5.opt ../materials/stdlib/obtaining-resources.py gem5 Simulator System. http://gem5.org gem5 is copyrighted software; use the --copyright option for details.

gem5 version 21.2.0.0

gem5 compiled May 16 2022 12:37:27

gem5 started May 16 2022 12:46:24

gem5 executing on liberty.cs.ucdavis.edu, pid 305928

command line: ./build/X86/gem5.opt ../materials/stdlib/obtaining-resources.py

The resources is available at /home/bbruce/.cache/gem5/riscv-disk-img

The stdlib will use the cached resources if already downloaded.

# Using a Custom Resource

You don't need to use the gem5 resources

You can specify a local resources (e.g., your own disk image)

- 1 from gem5.resources.resource import CustomResource

2

- 3 CustomResource("tests/test-progs/hello/bin/x86/linux/hello")

#### More detailed output

Look into the more the "gem5/m5out" directory

#### $\sim$ m5out

- $\equiv$  config.dot

- ✗ config.dot.pdf

- 🕤 config.dot.svg

- $\equiv$  config.ini

- {} config.json

- $\equiv$  stats.txt

- The "config" files detail your system configuration (various formats, "config.ini" most human-readable.

- The stats.txt shows the various simulation statistics.

- In Full-System simulations the terminal output can be found in this directory.

#### More detailed output

Look into the more the "gem5/m5out/stats.txt" file

| Simulation | Statistics |                       |

|------------|------------|-----------------------|

|            |            | 0.000005              |

|            |            | 4979349               |

|            |            | 4979349               |

|            |            | 1000000000000         |

|            |            | 0.08                  |

|            |            | 64410071              |

|            |            | 1169600               |

|            |            | 6546                  |

|            |            | 12944                 |

|            |            | 84513                 |

|            |            | 167067                |

|            | Simulation | Simulation Statistics |

# Modifying our design!

Remember: gem5 is modular!

In general, you can replace components with components of the same type.

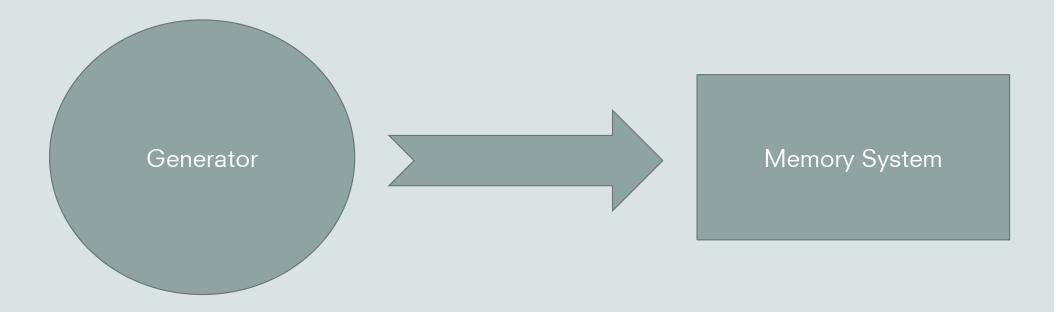

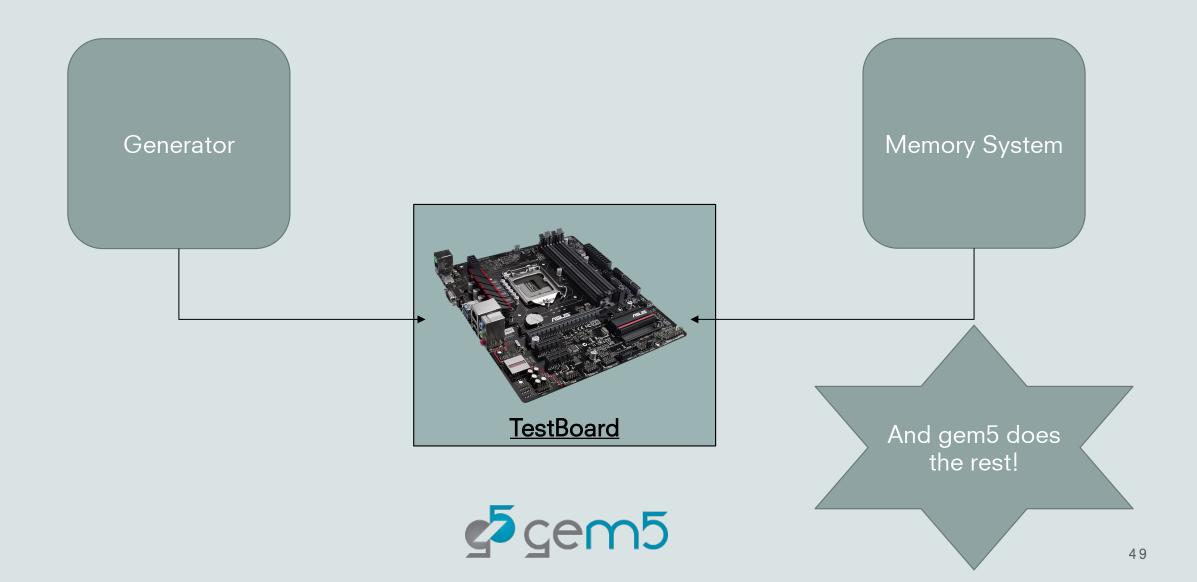

Let's convert our basic "hello world" board into a Traffic generator board.

#### **Traffic Generator**

#### The 'TestBoard'

#### Let's build one!

Go to "materials/traffic-generator.py"

Here we have imports, and some boilerplate code to run the simulation. You're code will go in-between.

# Traffic generator: Setup our components

| 9  | <pre># Setup the components.</pre>                 |

|----|----------------------------------------------------|

| 10 | <pre>memory = SingleChannelDDR3_1600("1GiB")</pre> |

| 11 | generator = RandomGenerator(                       |

| 12 | duration="250us",                                  |

| 13 | rate="40GB/s",                                     |

| 14 | num_cores=1,                                       |

| 15 | <pre>max_addr=memory.get_size(),</pre>             |

| 16 | )                                                  |

| 17 | cache_hierarchy = NoCache()                        |

# Traffic generator: Connect them to the TestBoard

| 19 | # Add them to the Test board.               |

|----|---------------------------------------------|

| 20 | board = TestBoard(                          |

| 21 | clk_freq="3GHz",                            |

| 22 | generator=generator,                        |

| 23 | memory=memory,                              |

| 24 | <pre>cache_hierarchy=cache_hierarchy,</pre> |

| 25 | )                                           |

## Running the traffic generator.

#### > gem5 materials/traffic-generator.py

This should be quite fast. What have we done?

Generated traffic to evaluate a memory component This does not require a workload or even a real processor

Users would typically consult the stats.txt

### Let's add a 'fun' memory system

from gem5.components.memory import HBM2Stack

Complete version can be found in "materials/complete/traffic-generator-hbm2stack.py" 2<sup>nd</sup> generation High Bandwidth Memory stack

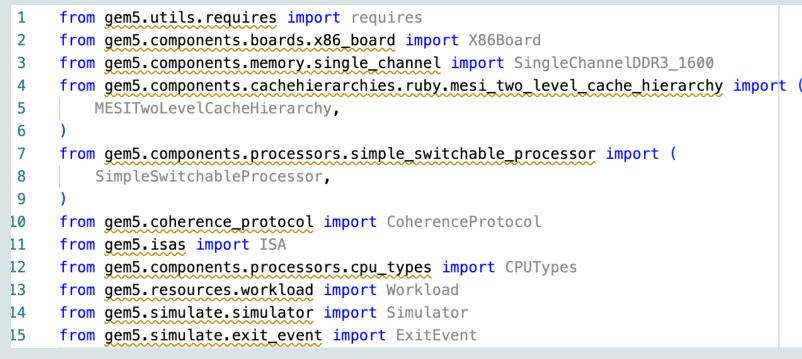

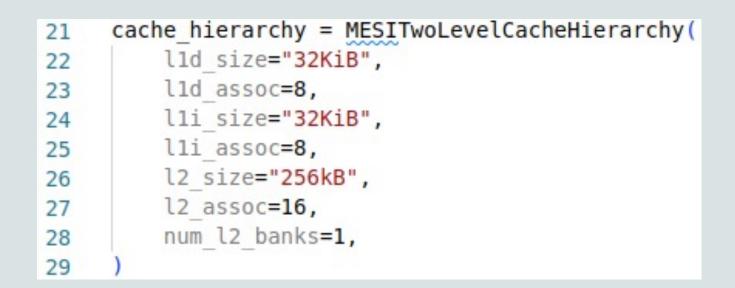

# More complex designs: An X86 full system simulation in the stdlib

Move to "materials/x86-full-system.py. You should see the following provided for you:

# Adding the 'requires' function

| 15 | requires(                                                                |

|----|--------------------------------------------------------------------------|

| 16 | <pre>isa_required=ISA.X86,</pre>                                         |

| 17 | <pre>coherence_protocol_required=CoherenceProtocol.MESI_TWO_LEVEL,</pre> |

| 18 | )                                                                        |

This adds a check for the gem5 binary parsing the script. In this case:

- 1. The binary supports the X86 ISA.

- 2. The binary supports the MESI Two Level coherence protocol.

35 memory = SingleChannelDDR3\_1600("2GiB")

| 47 | processor = SimpleSwitchableProcessor(         |

|----|------------------------------------------------|

| 48 | <pre>starting_core_type=CPUTypes.TIMING,</pre> |

| 49 | <pre>switch_core_type=CPUTypes.03,</pre>       |

| 50 | num_cores=2,                                   |

| 51 | isa=ISA.X86,                                   |

| 52 | )                                              |

|    |                                                |

The SimpleSwitchingProcessor allows for different types of cores to be swapped during a simulation with `processor.switch()`.

This can be useful when wanting to switch to and from a detailed form of simulation. (Timing = less detailed but fast; O3 = detailed but slow).

| 50 | board = X86Board(                           |

|----|---------------------------------------------|

| 51 | clk_freq="3GHz",                            |

| 52 | processor=processor,                        |

| 53 | memory=memory,                              |

| 54 | <pre>cache_hierarchy=cache_hierarchy,</pre> |

| 55 | )                                           |

As usual, we add the components to the board, in this case an `X86Board`.

#### workload = Workload("x86-ubuntu-18.04-boot")

```

"resources": [

{

"type" : "workload",

"name" : "x86-ubuntu-18.04-boot",

"documentation" : "A full boot of Ubuntu 18.04 with Linux 5.4.49

for X86. It runs an `m5 exit` command when the boot is completed unless the

readfile is specified. If specified the readfile will be executed after

booting.",

"function": "set_kernel_disk_workload",

"resources" : {

"kernel" : "x86-linux-kernel-5.4.49",

"disk_image":"x86-ubuntu-18.04-img"

},

"additional_params" : {}

}

}

```

http://resources.gem5.org/resources.json

| 105 |                                                                 |

|-----|-----------------------------------------------------------------|

| 105 | command = (                                                     |

| 106 | "m5 exit;"                                                      |

| 107 | + "echo 'This is running on 03 CPU cores.';"                    |

| 108 | + "sleep 1;"                                                    |

| 109 | + "m5 exit;"                                                    |

| 110 | )                                                               |

| 111 |                                                                 |

| 112 | <pre>workload.set_parameter("readfile_contents", command)</pre> |

#### board.set\_workload(workload)

#### **Exit Events**

**Note:** This is module is still considered to be in Beta. The API may change in future versions of gem5

| 19 | command = | <mark>"m5 exit;</mark> " \                                 |

|----|-----------|------------------------------------------------------------|

| 20 | +         | "echo 'This is running on Timing CPU cores.';" $\setminus$ |

| 21 | +         | "sleep 1;" \                                               |

| 22 | +         | "m5 exit;"                                                 |

During a simulation you can have "Exit Events".

In this example there are two. These return the simulation to the Python Script.

# The Simulation Loop

# The Simulator Module handles the loop!

```

31 simulator = Simulator(board=board)

32

33 simulator.run() # Runs up to the first `m5 exit`` event`

34

35 # Here we can do things between the exit event

36

37 processor.switch()

38

39 simulator.run() # Run up to the final `m5 exit` event

```

Here we can run up to an exit event, do things, and then continue the run.

In this case we want to switch the CPU cores.

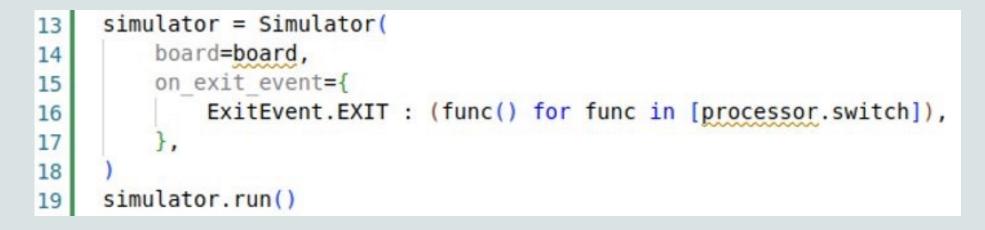

# The Simulator Module: We can do better

Here we can specify exactly what to do on each exit event type via Python generators.

The Simulator had default behavior for these events, but they can be overridden.

- ExitEvent.EXIT

- ExitEvent.CHECKPOINT

- ExitEvent.FAIL

- ExitEvent.SWITCHCPU

- ExitEvent.WORKBEGIN

- ExitEvent.WORKEND

- ExitEvent.USER\_INTERRUPT

- ExitEvent.MAX\_TICK

# Your done! You can now run your fullsystem simulation

Warning: This will take a long time to complete execution.

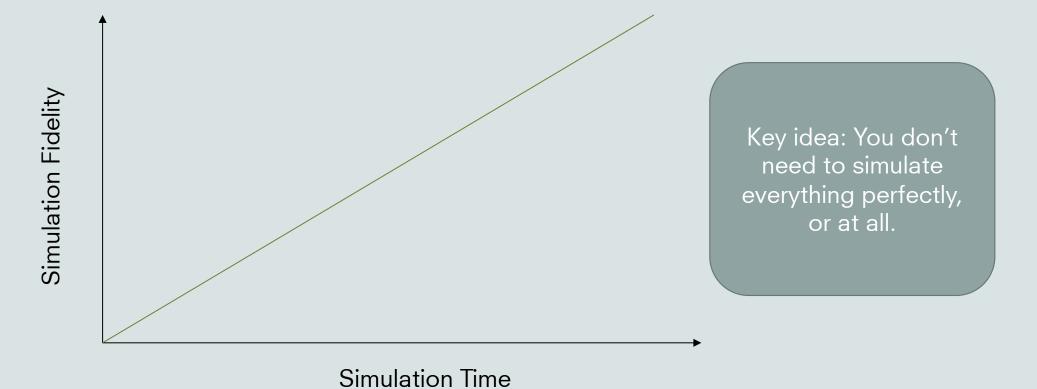

#### Simulation's major pitfall: It's slloooww

#### Fortunately, there are some work arounds

#### Some techniques we provide

#### Simpoints/Looppoints

There's a tutorial on Looppoints this afternoon in Outremont 1

Discuss: What is a Simpointing?

#### Open "materials/simpoints-checkpoint.py"

| 35 | <pre># Setup the Simpoints workload</pre>            |

|----|------------------------------------------------------|

| 36 | <pre>board.set_se_simpoint_workload(</pre>           |

| 37 | <pre>binary=obtain_resource("x86-print-this"),</pre> |

| 38 | arguments=["print this", 15000],                     |

| 39 | <pre>simpoint=SimpointResource(</pre>                |

| 40 | <pre>simpoint_interval=1000000,</pre>                |

| 41 | simpoint_list=[2, 3, 4, 15],                         |

| 42 | weight_list=[0.1, 0.2, 0.4, 0.3],                    |

| 43 | <pre>warmup_interval=1000000,</pre>                  |

| 44 | ),                                                   |

| 45 | )                                                    |

```

dir = Path("simpoint-checkpoint-dir")

47

48

dir.mkdir(exist_ok=True)

49

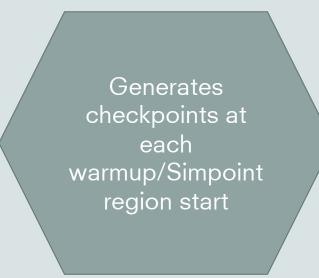

# Here we use the Simpoints generator to take the checkpoints.

50

51

# When a Simpoint region, or warmup region, begins, a checkpoint is generated.

simulator = Simulator(

52

53

board=board,

on_exit_event={ExitEvent.SIMPOINT_BEGIN: save_checkpoint_generator(dir)},

54

55

56

```

#### > gem5 materials/simpoint-checkpoint.py

#### Simpoints: Restoring

#### > gem5 materials/simpoints-restore.py

#### The gem5 GPU Model

#### Caveats

gem5 is a tool, not a panacea

Most models are not validated against "real" hardware

See "Architectural Simulators Considered Harmful"

There are bugs!

# Getting (more) help

Main gem5 website: <u>http://gem5.org/</u> More like this:

https://www.gem5.org/documentation/ learning\_gem5/introduction/

Mailing lists: <u>http://gem5.org/Mailing\_Lists</u> *gem5-users:* General user questions (you probably want this one) *gem5-dev:* Mostly code reviews and highlevel dev talk

gem5 slack: https://join.slack.com/t/gem5workspace/shared invite/zt-1c8go4yjo-LNb7I~BZ0FagwmVxX08y9g

#### References

- Martin et al. 2005. Multifacet's general execution-driven multiprocessor simulator (GEMS) toolset. ACM SIGARCH Computer Architecture News. <u>https://doi.org/10.1145/1105734.1105747</u>

- Binkert et al. 2006. The M5 simulator: Modeling Networked Systems. IEEE Micro. https://doi.org/10.1109/MM.2006.82

- Binkert, et al. 2011. The gem5 simulator. SIGARCH Comput. Archit. News 39 http://dx.doi.org/10.1145/2024716.2024718

- Lowe-Power et al 2021. The gem5 Simulator: Version 20.0+. ArXiv Preprint ArXiv:2007.03152, 2021. <u>https://doi.org/10.48550/arXiv.2007.03152</u>